This repository contains the source code for VLSI CAD Project, Domain Specific Hardware Accelerators, as apart of coursework in

CS6230 : CAD for VLSI.

Fall, 2020.

The following components are implemented in Bluespec System Verilog:

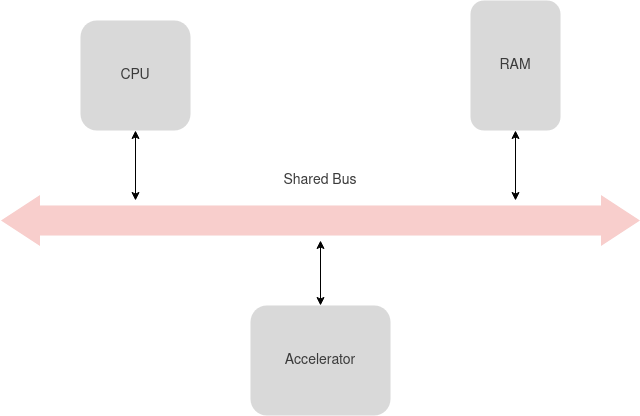

- CPU

- RAM

- Bus

- Vector Processor

A minimal 2 stage pipelined inorder processor.

A vector processor capable of:

- Vector Negation (int8, int16, int32, float32)

- Vector Minima (int8, int16, int32, float32)

See https://arm-software.github.io/CMSIS_5/DSP/html/group__groupMath.html for details about the functions.

A minimal custom bus for demonstration.

See Final Report.pdf